Gen-Z is a very new interconnect consortium that is focused on newer, advance memory, storage and accelerator architectures and devices. Gen-Z is based on the IEEE-802.3 physical layer specifications and external interconnects like SFP28 and QSFP28 connectors, cables and modules. Its first generation data transfer speed rate is 25Gbps per lane. 56GT/s and 112GT/s speed rate technologies and products are in various stages of research and development. Will Gen-Z networking fabric links soon be competing versus PCIe, Ethernet and InfiniBand fabric links?

This consortium will be developing specifications that will include new connectors, modular form-factors and related thermal cooling systems. The internal connectors will be used for connecting new types of components and sub-assemblies like 3-D memory, NVM modules, FPBAs, GPUs, GPU/CPUs, DSPs, IOs and NICs. It is not often that there is a new interconnect standard subcommittee that is requesting new high speed IO connector proposals!

This consortium will be developing specifications that will include new connectors, modular form-factors and related thermal cooling systems. The internal connectors will be used for connecting new types of components and sub-assemblies like 3-D memory, NVM modules, FPBAs, GPUs, GPU/CPUs, DSPs, IOs and NICs. It is not often that there is a new interconnect standard subcommittee that is requesting new high speed IO connector proposals!

This consortium is currently led by AMD, ARM, Broadcom, Cavium, Cray, Dell EMC, HPE, Huawei, IDT, Lenovo, Mellanox, Micro-semi, RedHat, Samsung, Seagate, SK-Hynix, Western Digital and Xilinix. It probably has several more, early joiner companies getting ready to join as this blog is posted as it was just announced publicly last week.

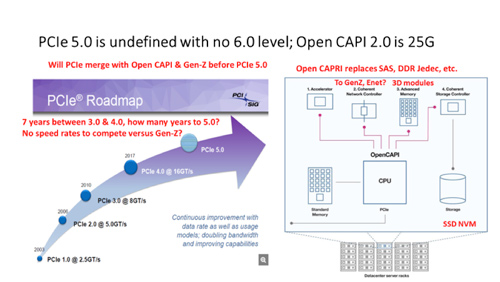

Gen-Z 1.0 25GT/s and 28GT/s IO interfaces compete with the new but slower PCIe 4.0 architecture that is just becoming available and starting to run at 16Gbps per lane. Gen-Z architecture supports 1-256 lanes versus PCIe supporting 1-48 lanes however most links will be likely to have 1, 2, 4, 8, 12 and 16 lane implementations. The PCIe roadmap stops at PCIe 5.0 32G while the Gen-Z scales from 56GT/s, 112GT/s and higher.

Gen-Z interconnect also works with the new Open CAPRI consortium inside the box interconnect standard.

There is an industry open question of whether these two consortiums’ interconnects dominate the market versus PCIe or will they merge together becoming yet another newer standard like FIO and NGIO merged to become InfiniBand, the very low latency server and system Fabric network that is very popular especially within the HPC market segment.

So, there will be new connector standards for advance memory modules especially 3D stack types and Serdes connections versus the older single ended DDR wide parallel traditional types. Also, there will likely be new connectors for plugging NVM storage modules. It appears that this new interconnect effort will cause the SATA-SSD, SAS HDD and interface markets to shrink precipitously within two to three years. New modules will be able to be inserted from top to bottom or horizontally into an array board. A portion of power will be distributed thru the new connectors and thru separate power cable cords.

Noticably not on the Gen-Z developers list yet are companies like Intel, Microsoft and Cisco.

Will PCI-SIG consortium work with Open CAPRI and Gen-Z as they use the same form-factors, connector and cable assembly types, even if their protocols remain independent or vice versa?

Even now at the intra-chip, intra SOIC and inter-chip circuit level, Intel’s QPI, Quick Path Interconnect, a chip to chip connection architecture has new competition as the CCIX consortium is developing a new architecture and standard that is in harmony with the new Gen-Z and Open CAPRI standards.

Leave a Reply

You must be logged in to post a comment.