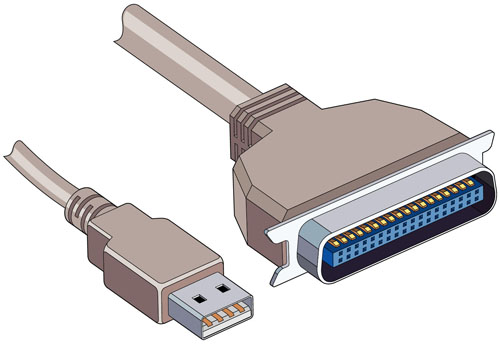

Parallel architectures have been around for a long time, both in backplane architectures and IO protocols. Slowly but surely they are being displaced by serial protocols. You probably remember the old printer cables that used many pins in parallel. Compare that to the USB connections used to connect many peripherals today using serial architecture.

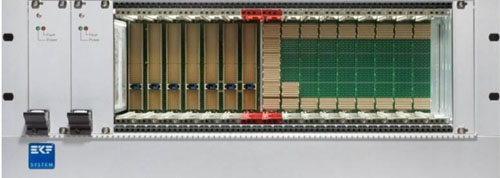

Parallel backplane architectures have been used in industry-standard chassis architectures such as VMEbus and Compact PCI (CPCI) since the 1980s. In essence, these architectures have simple backplanes with traces connecting each pin position on every connector to the same signal. The backplane layer count was low (one layer for each connector row, three layers for VME or five layers for CPCI.) This created an extremely flexible, low-cost system. It also meant that any card could be in any slot in a system and that system designers can ship a basic system with many empty slots that can be later filled by the end user as they add functionality and more ports in their systems. This architecture also facilitates use of very small chassis with only a few slots.

These parallel architectures have dominated many industry segments for years, finding many uses in communication, factory monitoring and control systems, Military, and medical.

The limitation of parallel systems is the speed of individual signal traces. Each pin in the chain creates an electrical stub that attenuates the height and “squareness” of the signal pulse and reflects part of the signal as well. By using 32- and 64-bit wide connectors, systems designers can achieve 40 Mbyte/s using parallel architecture. Subsequent developments have resulted in much faster systems, generally by adding serial technology that coexists with the parallel bus.

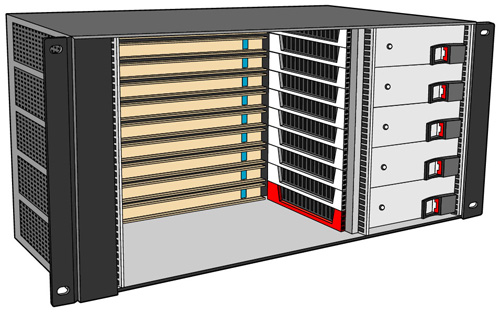

Serial architectures take an entirely different approach. Rather than expanding chassis bandwidth by adding more pins, serial chips transmit over fewer signal pairs at much higher speeds. These higher speed signals need a dedicated trace pair for each transmit-receive link. This point-to-point connection will go through the fewest number of connectors possible. Connectors become smaller, but the backplanes become more complex, with more signal layers to enable high speed signals to cross over each other on different layers. Today all high-speed systems use serial architecture.

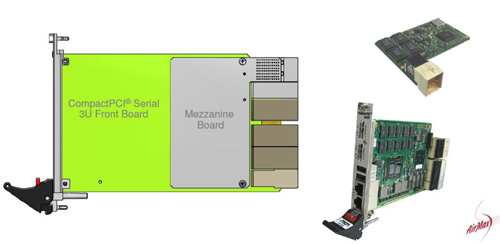

Both VME and CPCI have augmented their parallel bus structure with serial architectures through many generations of standards to keep up to date with their customer’s requirements. One of the more clever implementations combining serial and parallel is the CompactPCI Serial Architecture. By choosing the protocol, systems designers can design boxes that run state-of-the-art Ethernet, SAS, SCSI, or Infiniband, enabling powerful systems to exist in a relatively small chassis. One of the major applications for this architecture is in systems for communication and control in high-speed trains, ships, and other transportation applications.

This particular backplane has connectors on the backplane that can mate to a right angle receptacle Daughtercard connector, and an accurately placed right angle connector on the mezzanine card at the same time.

By choosing wisely, system architects can take advantage of both parallel and serial architectures to create systems ideally suited for their intended application at the right cost.

Leave a Reply

You must be logged in to post a comment.